## International Research Journal of Modernization in Engineering Technology and Science

(Peer-Reviewed, Open Access, Fully Refereed International Journal)

Volume:05/Issue:10/October-2023 Impact Factor- 7.868

www.irjmets.com

# HARDWARE STRATEGIES FOR NETWORK OPTIMIZATION SUPPORTING AI WORKLOADS

## Sudheer Kandula<sup>\*1</sup>, Sree Ranga Vasudha Moda<sup>\*2</sup>

\*1Senior Software Engineer, Nvidia, Santa Clara, CA, USA.

\*<sup>2</sup>Lead Member Of Technical Staff, Salesforce, San Francisco, CA, USA.

DOI: https://www.doi.org/10.56726/IRJMETS45389

## ABSTRACT

Network optimization is indispensable for AI workloads as it accelerates data transfer, reduces model training time, and minimizes inference latency. Efficient network utilization ensures scalability, maximizes resource utilization, and enhances cost efficiency by minimizing infrastructure requirements. This is particularly crucial in the era of distributed and edge computing, where seamless communication between nodes and devices is essential for the smooth functioning of AI applications. In essence, network optimization is a linchpin for realizing the full potential of AI, influencing both the speed and cost-effectiveness of model development, training, and real-time inference.

This paper dives deep into the Hardware Strategies for Network Optimization, focusing on their pivotal role. Within the hardware domain, we explore strategies like Memory, Storage, Accelerators, Network device selection. These perspectives offer a comprehensive understanding of the intricacies involved in achieving efficient communication and collaboration of massive workloads. The paper provides valuable insights into the nuances of network optimization, aiming to empower organizations to unleash the full potential of AI technologies.

Keywords: Artificial Intelligence, Network Optimization, Memory, Storage, Accelerators.

## I. INTRODUCTION

Artificial Intelligence (AI) encompasses the development of computer systems with human-like intelligence, enabling them to perform complex tasks. Network efficiency is integral to AI's success, as it ensures the seamless flow of data between components, facilitates real-time processing for applications like autonomous systems, promotes collaboration among distributed elements, supports scalability to handle growing datasets, minimizes latency for quicker responses, optimizes resource utilization, and contributes to overall cost-effectiveness. In essence, network efficiency is a cornerstone in maximizing the functionality and potential of AI systems across diverse applications and domains.

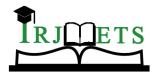

Figure 1: Intricate workflow that underlies the AI paradigm.

@International Research Journal of Modernization in Engineering, Technology and Science [1549]

# International Research Journal of Modernization in Engineering Technology and Science (Peer-Reviewed, Open Access, Fully Refereed International Journal)

Volume:05/Issue:10/October-2023 Impact Factor- 7.868

www.irjmets.com

Figure 1 serves as a visual testament to the intricate workflow that underlies the AI paradigm, where the journey from raw data to meaningful insights traverses a carefully orchestrated path. shedding light on how structured and unstructured data undergo a meticulous process of collection, conditioning, curation, and labeling before being entrusted to the capable hands of AI algorithms. AI algorithms transmute raw data into actionable knowledge. This knowledge, in turn, becomes the linchpin in the dynamic collaboration between humans and machines, exemplified by the concept of Human-Machine Teaming. In this paradigm, insights gleaned from AI algorithms are seamlessly integrated into user missions and various AI applications, thereby enhancing decision-making processes and driving innovation across diverse domains.

However, the efficacy of this intricate workflow is contingent upon the seamless orchestration of modern computing resources. Every segment of the AI workflow relies heavily on a sophisticated computing layer, comprising Accelerators (CPUs, GPUs, TPUs, etc.), network devices, storage drives, and memory. If not managed judiciously, the computing infrastructure can become a bottleneck, impeding the otherwise fluid progression of data to insights. Thus, a strategic approach to optimizing computing resources for enhanced performance becomes paramount.

This paper aims to unravel the complexities surrounding the optimization of the modern computing layer in the context of AI workflows. By exploring strategies to mitigate bottlenecks and enhance the efficiency of computing resources, we seek to pave the way for a smoother, more streamlined AI workflow. Through an indepth examination of the role played by different components within the computing layer, including accelerators, network devices, storage drives, and memory, we present a comprehensive guide to navigating the intricate landscape of AI-powered computing.

# II. HARDWARE DESIGN STRATEGIES FOR NETWORK OPTIMIZATION

Optimizing network bandwidth is crucial for efficient communication, especially in scenarios where resources are limited or expensive. In our research, we identified a list of Software strategies [1] and hardware strategies that can help achieve optimized network bandwidth usage, categorized under various hierarchical segregations.

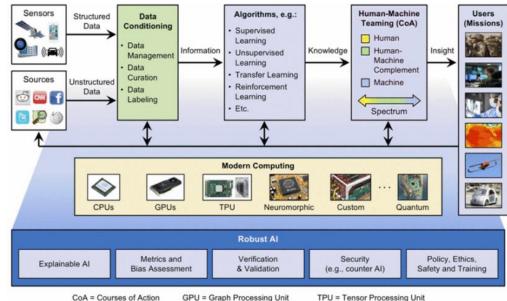

Figure 2: Layers in building Hardware for AI/ML Applications

## Memory:

Memory [2] serves as the neural nexus for Artificial Intelligence (AI) operations, facilitating short-term storage during processing. The imperative for swift data access in iterative computations necessitates advanced solutions like DRAM and NAND Flash memory from players such as Samsung, Micron, and SK Hynix. In addition to DRAM and NAND Flash memory, STT-MRAM, ReRAM, PCRAM, FeRAM, and 3D XPoint Memory are expected to be available for better speed and performance.

## Storage:

In the realm of AI with Petabytes of data involved, efficient data handling is contingent on high-performance storage [3] solutions. Traditional Hard disk drives (HDDs) and network-attached storage (NAS) devices may struggle to keep up with the scale and performance needed.to address this challenge we can turn to high storage solutions like Solid State Drives (SSDs) and All flash arrays (AFAs), NAND Flash storage, exemplified by cutting-edge NVMe Solid state drives (SSDs) like the Samsung 980 PRO and WD Black SN850, can provide the seamless access and retrieval of colossal datasets. These SSDs distinguish themselves with accelerated read and write operations, imparting a tangible impact on the speed at which AI models process information. The rapid

# International Research Journal of Modernization in Engineering Technology and Science (Peer-Reviewed, Open Access, Fully Refereed International Journal)

Volume:05/Issue:10/October-2023 Impact Factor- 7.868

www.irjmets.com

retrieval of datasets is a cornerstone in AI applications. Some organizations are also exploring the use of storage-class memory (SCM) technologies, which combine the speed of DRAM with the persistence of NAND flash, offering even greater performance improvements.

## Accelerators:

The Accelerators, comprising Central Processing Units (CPUs), Graphics Processing units (GPUs), Field-Programmable Gate Array (FPGAs), and Application specific integrated circuits (ASICs), delineates the computational provess underpinning AI endeavors.

## CPU (Central Processing Unit):

Central processing units (CPUs) excel in versatility, accommodating diverse computing needs. They are wellsuited for tasks requiring sequential processing. Intel Core i9 and AMD Ryzen stand out as formidable Central Processing units (CPUs), balancing general-purpose computing with AI-specific optimizations. Limitations of central processing units (CPUs) include challenges in handling parallel tasks efficiently, potentially impacting performance in certain Artificial Intelligence (AI) workloads.

## GPU (Graphics Processing Unit):

Graphics processing units (GPUs) [4] are paragons of parallel processing, rendering them indispensable for computationally intensive tasks, NVIDIA GeForce and Quadro series represent pinnacle Graphics processing unit (GPU) technology, excelling in parallel processing for neural network operations. Limitations include higher power consumption and potential inefficiency for non-parallel tasks.

## FPGA (Field Programmable Gate Array):

Field Programmable Gate Arrays (FPGAs) [5] shine in their programmability, offering adaptability for customizing AI workloads to specific requirements, Xilinx and Intel offer leading-edge Field Programmable Gate Arrays (FPGAs), providing flexibility through programmability. Limitations include the learning curve associated with Field Programmable Gate Arrays (FPGAs) and potential resource limitations for complex tasks.

## ASIC (Application Specific Integrated Circuit):

Application specific integrated circuit (ASICs) [6] emerge as purpose-built powerhouses, delivering optimal performance for highly efficient specialized tasks in AI. Google Tensor Processing Unit (TPU) and Bitmain Antminer exemplify Application specific integrated circuit (ASIC) efficiency, designed for highly specialized AI tasks. Limitations include a lack of flexibility for tasks beyond their designated scope and potential higher development costs.

The choice of logic component is a nuanced decision, intricately tied to the demands of the AI workload, balancing performance requirements with the inherent trade-offs and limitations of each technology.

## Networking:

## **Programmable Switches:**

Programmable switches [7] play a pivotal role in orchestrating the flow of data within AI ecosystems. Noteworthy products in this category, such as Barefoot Tofino and P4-programmable switches, are distinguished by their programmability. This characteristic enables network engineers to tailor switch behavior according to specific AI workload requirements, optimizing data transfer within the network. Programmable switches are prized for their adaptability, allowing for dynamic adjustments to accommodate evolving AI applications and varying traffic patterns. The agility and customization offered by these switches contribute to the overall efficiency and responsiveness of AI networks.

## Data Processing Units (DPUs):

Data Processing Units (DPUs) [8] emerge as a specialized category designed to enhance in-line processing efficiency. Products like NVIDIA Bluefield and Smart Network Interface cards (smart NICs) equipped with Data Processing Units (DPUs) integrate computational power directly into the network interface. This integration enables tasks such as packet processing and security functions to be offloaded from the central processing unit (CPU), freeing it for more complex Artificial Intelligence (AI) computations. Data Processing Units (DPUs) excel in accelerating data-centric operations, reducing latency, and enhancing overall system performance. Their ability to seamlessly integrate with existing infrastructure positions Data Processing Units (DPUs) as a strategic component in modern AI hardware architectures.

## International Research Journal of Modernization in Engineering Technology and Science (Peer-Reviewed, Open Access, Fully Refereed International Journal)

Volume:05/Issue:10/October-2023 Impact Factor- 7.868

www.irjmets.com

#### High Speed Interconnect:

High Speed Interconnect (HSI) [9] technologies serve as the lifeline for seamless communication between various components within an Artificial Intelligence (AI) ecosystem. Exemplary solutions, including InfiniBand and Ethernet with RDMA, set the stage for rapid and low-latency data exchange. The choice of a high-speed interconnect is paramount in scenarios where large datasets traverse between storage, memory, and processing units. Metrics such as latency, measured in microseconds, and data transfer rates, measured in terabits per second (Tbps), become critical in ensuring the swift and efficient movement of data. High-speed interconnects provide the necessary bandwidth and responsiveness to support the intricacies of Artificial Intelligence (AI) workloads.

In summary, these advanced components Programmable Switches, Data Processing Units (DPUs), and High-Speed Interconnects (HSI) augment the foundational pillars of AI hardware. Programmable switches bring flexibility and customization to network orchestration, Data Processing Units (DPUs) streamline in-line processing for optimal efficiency, and high speed interconnects (HIS) form the agile conduits for rapid data exchange.

As AI applications diversify and intensify, the strategic integration of these advanced components becomes imperative for architects and engineers seeking to push the boundaries of Artificial Intelligence (AI) hardware capabilities. synthesis, these four categories Memory, Storage, Logic, and Networking alongside their subcategories, not only form the bedrock of advanced AI hardware but represent strategic choices that profoundly impact system performance and responsiveness. This exploration illuminates the multifaceted considerations that underpin each category, offering a comprehensive framework for architects and engineers to navigate the complexities of AI hardware decisions. As AI continues its ascent, the astuteness in selecting and integrating these hardware strategies will undeniably chart the trajectory of success in the evolving landscape of artificial intelligence.

## III. CONCLUSION

In conclusion, optimizing network bandwidth emerges as a critical facet in enhancing communication efficiency, particularly in resource-constrained or cost-sensitive scenarios. Through our research, we have delineated hardware strategies across various hierarchical levels that contribute to achieving optimized network bandwidth usage. The exploration of Memory, Storage, Logic (comprising CPU, GPU, FPGA, and ASIC), and Networking components has revealed a nuanced decision-making process, where each category plays a pivotal role in shaping the bedrock of advanced AI hardware. Memory solutions such as DRAM and NAND Flash, high-performance storage options like SSDs and AFAs, and diverse Logic components including CPUs, GPUs, FPGAs, and ASICs each present unique strengths and limitations. Furthermore, the role of Networking components, such as Programmable Switches, Data Processing Units (DPUs), and High-Speed Interconnects (HSI), is crucial in optimizing data flow within AI ecosystems. As AI applications evolve, the strategic integration of these advanced components becomes imperative for architects and engineers aiming to push the boundaries of AI hardware capabilities. The comprehensive framework provided by our exploration offers valuable insights for navigating the complexities of AI hardware decisions, emphasizing that the astuteness in selecting and integrating these hardware strategies will undeniably influence the trajectory of success in the continually evolving landscape of artificial intelligence.

# **IV. FUTURE WORK**

Network optimization strategies for Compute, Application and Security fronts would be extensions to this research and coming up in the future.

## V. REFERENCES

- [1] Sudheer Kandula, Sree Ranga Vasudha Moda, "Software Data Strategies for Network Optimization supporting AI workloads", International Research Journal of Modernization in Engineering Technology and Science, Volume:05/Issue:10/October-2023, https://www.doi.org/10.56726/IRJMETS45318.

- [2] J. Choe, "Memory Technology 2021: Trends & Challenges," 2021 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Dallas, TX, USA, 2021, pp. 111-115, doi: 10.1109/SISPAD54002.2021.9592547.

# International Research Journal of Modernization in Engineering Technology and Science (Peer-Reviewed, Open Access, Fully Refereed International Journal)

| volume:05/1ssue:10/October-2025 Impact Factor-7.000 www.frmets.com | Volume:05/Issue:10/October-2023 | Impact Factor- 7.868 | www.irjmets.com |

|--------------------------------------------------------------------|---------------------------------|----------------------|-----------------|

|--------------------------------------------------------------------|---------------------------------|----------------------|-----------------|

- [3] Jaeyoung Do, Victor C. Ferreira, Hossein Bobarshad, Mahdi Torabzadehkashi, Siavash Rezaei, Ali Heydarigorji, Diego Souza, Brunno F. Goldstein, Leandro Santiago, Min Soo Kim, Priscila M. V. Lima, Felipe M. G. França, and Vladimir Alves. 2020. Cost-effective, Energy-efficient, and Scalable Storage Computing for Large-scale AI Applications. ACM Trans. Storage 16, 4, Article 21 (November 2020), 37 pages. https://doi.org/10.1145/3415580

- [4] André R. Brodtkorb, Trond R. Hagen, Martin L. Sætra, Graphics processing unit (GPU) programming strategies and trends in GPU computing, Journal of Parallel and Distributed Computing, Volume 73, Issue 1,2013,Pages 4-13,ISSN 07437315,https://doi.org/10.1016/j.jpdc.2012.04.003.

- [5] J. Rose and S. Brown, "Flexibility of interconnection structures for field-programmable gate arrays," in IEEE Journal of Solid-State Circuits, vol. 26, no. 3, pp. 277-282, March 1991, doi: 10.1109/4.75006.

- [6] C. F. Fey and D. E. Paraskevopoulos, "A techno-economic assessment of application-specific integrated circuits: Current status and future trends," in Proceedings of the IEEE, vol. 75, no. 6, pp. 829-841, June 1987, doi: 10.1109/PROC.1987.13804.

- [7] James McCauley, Aurojit Panda, Arvind Krishnamurthy, and Scott Shenker. 2019. Thoughts on load distribution and the role of programmable switches. SIGCOMM Comput. Commun. Rev. 49, 1 (January 2019), 18–23. https://doi.org/10.1145/3314212.3314216.

- [8] L. Barsellotti, F. Alhamed, J. J. Vegas Olmos, F. Paolucci, P. Castoldi and F. Cugini, "Introducing Data Processing Units (DPU) at the Edge [Invited]," 2022 International Conference on Computer Communications and Networks (ICCCN), Honolulu, HI, USA, 2022, pp. 1-6, doi: 10.1109/ICCCN54977.2022.9868927.

- [9] W. T. Beyene, "Application of Artificial Neural Networks to Statistical Analysis and Nonlinear Modeling of High-Speed Interconnect Systems," in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 26, no. 1, pp. 166-176, Jan. 2007, doi: 10.1109/TCAD.2006.882518.