International Research Journal of Modernization in Engineering Technology and Science (Peer-Reviewed, Open Access, Fully Refereed International Journal)

Volume:07/Issue:03/March-2025

**Impact Factor- 8.187**

www.irjmets.com

## DATA CENTER DESIGN FOR AI AND AI FOR DATA CENTER DESIGN

## Aditya Avinash Atluri\*1

\*1The George Washington University, USA.

DOI: https://www.doi.org/10.56726/IRJMETS68972

#### **ABSTRACT**

This article examines the specialized approach to data center design for artificial intelligence applications, particularly Large Language Models. It explores how optimizing infrastructure for specific computational needs significantly enhances efficiency and performance across different stages of the machine learning lifecycle: pretraining, fine-tuning, and inference. The article details the hardware and software components crucial for AI workloads, highlighting the evolution of GPU technology and its vital role in accelerating complex matrix operations. The article also discusses server-level architectures, communication systems between processing units, and optimization techniques for training and inference. Additionally, it reveals how AI is being leveraged to improve various aspects of data center operations, from resource management to predictive maintenance, creating a recursive relationship where AI enhances the infrastructure designed to support it.

**Keywords:** Infrastructure Optimization, GPU Acceleration, Distributed Computing, Machine Learning Lifecycle, Resource Management.

### I. INTRODUCTION

Before delving into data center design, it is essential to examine the characteristics of the application first. Optimizing a data center to align with the specific requirements of an application significantly enhances cost efficiency, performance, and power consumption, ultimately driving higher revenue. A comparison between Meta's (Facebook, WhatsApp, Instagram, Threads, etc.) datacenter architecture and that of cloud service providers (CSPs) such as Google Cloud Platform (GCP), Amazon Web Services (AWS), and Microsoft Azure highlights these differences[1]. Meta's infrastructure is tailored to support social networking applications with specific performance demands, whereas CSPs must accommodate a diverse range of applications with widely varying requirements. If Meta were to design its data centers like a CSP, it would incur substantial inefficiencies—either by under-provisioning or over-provisioning resources—resulting in increased operational costs and an inability to meet critical user experience metrics such as latency, recommendation accuracy, and bandwidth.

## II. THE MACHINE LEARNING LIFECYCLE: PRE-TRAINING, FINE-TUNING, AND INFERENCE

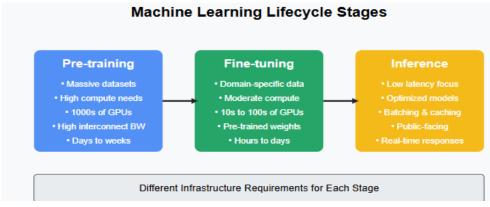

When designing data centers for machine learning workloads, particularly Large Language Models (LLMs), it is crucial to determine which phase of the machine learning lifecycle the data center will support. The computational and storage demands vary significantly across stages, from model development to deployment. The different stages of machine learning are pre-training, fine-tuning (post-training), and inference (deployment) [2]

Fig 1: Machine Learning Lifecycle Stages [2]

International Research Journal of Modernization in Engineering Technology and Science (Peer-Reviewed, Open Access, Fully Refereed International Journal)

Volume:07/Issue:03/March-2025 Impact Factor- 8.187 www.irjmets.com

### **Pre-training Infrastructure Requirements**

The first stage of building an LLM is pre-training, where researchers define the model architecture based on extensive experimentation to optimize performance across benchmarks and human evaluations. In addition to the model itself, vast amounts of data—often reaching terabytes or more—must be curated and stored[3]. If used directly, raw data can degrade model quality; thus, a rigorous data preprocessing pipeline is necessary. Once curated, the dataset is stored on high-capacity storage servers before training begins.

Pre-training requires substantial computational resources, with thousands of compute servers orchestrating training while continuously loading data from storage servers and storing intermediate results. Beyond core training, additional processes such as health checks, node migration, and checkpointing play critical roles, though this discussion focuses primarily on training itself. LLM architectures have largely converged on transformer-based designs, where computational efficiency is paramount. Transformer layers, which dominate execution time, are composed primarily of matrix multiplications. Consequently, hardware optimized for high-throughput matrix operations—such as NVIDIA GPUs—outperforms traditional CPUs for this workload. These GPUs accelerate transformer layers and efficiently execute auxiliary non-transformer operations.

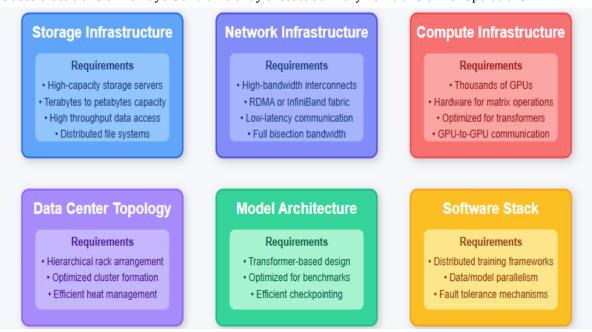

Fig 2: Pre-training Infrastructure Requirements [3]

#### **Hardware Architecture for LLM Training**

For a concrete example, consider Meta's LLaMA 3 model. According to their published research, LLaMA 3 was pre-trained on 15 trillion multilingual tokens, with the 405-billion-parameter variant utilizing 16,000 NVIDIA H100 GPUs. These GPUs were not simply pooled together for parallel execution but engaged in frequent inter-GPU communication due to the model's training architecture. After specific intervals, data from each GPU was redistributed to others, necessitating extremely high-bandwidth interconnects. Various networking technologies facilitate this communication. GPUs can communicate via PCIe, NVIDIA NVLink, or AMD Infinity Fabric within a single server. High-performance networking solutions such as RDMA over Converged Ethernet (RoCE) or InfiniBand are employed for inter-server connectivity. The optimal network topology depends on multiple factors, including cluster size, data center capacity, and the number of data centers participating in a training run. [4]

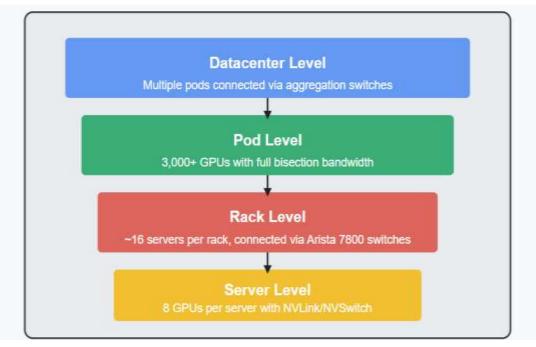

For LLaMA 3's 405B model, Meta utilized RoCE networking with Arista 7800 rack switches, while smaller models leveraged NVIDIA Quantum-2 InfiniBand fabric. The physical infrastructure was meticulously designed: each rack contained two eight-GPU servers, with 192 racks forming a 3,072-GPU pod featuring full bisection bandwidth to eliminate oversubscription. Eight such pods were interconnected at the highest level using aggregation switches to form a complete data center. Additionally, 7,500 high-speed storage servers, offering

## International Research Journal of Modernization in Engineering Technology and Science (Peer-Reviewed, Open Access, Fully Refereed International Journal)

Volume:07/Issue:03/March-2025

**Impact Factor- 8.187**

www.irjmets.com

240 petabytes of capacity with a sustained throughput of 2 TB/s (peaking at 7 TB/s), were deployed to store model checkpoints ranging from 1 MB to 4 GB per GPU [4].

Fig 3: Hardware Architecture for LLM Training [4]

### **Software Stack for Distributed Training**

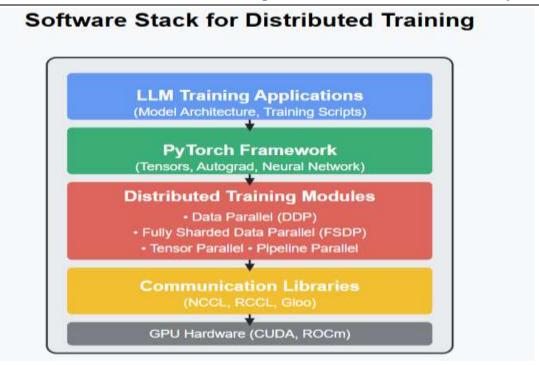

With hardware considerations addressed, the next crucial aspect of large-scale model training is the software stack that enables efficient computation, communication, and fault tolerance. At the core of modern deep learning workflows is PyTorch[5], an open-source machine learning framework that provides essential tools for training, fine-tuning, and inference. PyTorch is widely adopted due to its dynamic computation graph, ease of use, and strong support for research and production workloads. Originally developed by Meta, PyTorch has since become the foundation for training state-of-the-art models across academia and industry. PyTorch simplifies model development by offering a high-level abstraction for defining neural networks, managing tensors, and executing operations such as matrix multiplications, convolutions, and activation functions. However, training large-scale models—particularly those at the scale of modern large language models (LLMs)—introduces additional complexities. A single GPU lacks sufficient memory to store all model parameters, intermediate activations, and optimizer states, necessitating distributed training techniques. PyTorch provides a critical module, torch.distributed,[6] which enables multi-GPU and multi-node training by implementing several parallelization strategies. Distributed Data-Parallel (DDP) is the most commonly used approach, replicating the model across multiple GPUs and distributing different batches of data to each replica. Fully Sharded Data Parallel (FSDP) is a memory-efficient variant that shards model parameters and optimizer states across GPUs, reducing memory overhead and enabling the training of larger models. Tensor Parallelism (TP) splits individual layers—such as matrix multiplications—across multiple GPUs, reducing per-GPU memory requirements while maintaining compute efficiency. Pipeline Parallelism (PP) partitions the model into sequential stages, with different GPUs handling different network parts, improving scalability for extremely large models.

These distributed training techniques allow PyTorch to scale across thousands of GPUs, necessary for training models such as GPT, LLaMA, and other transformer-based architectures. Efficient inter-GPU communication is crucial, as large-scale models frequently require synchronization and parameter exchanges between devices. Technologies such as NVIDIA's NCCL (NVIDIA Collective Communications Library) optimize collective communication operations to minimize latency and maximize throughput during training.

International Research Journal of Modernization in Engineering Technology and Science (Peer-Reviewed, Open Access, Fully Refereed International Journal)

Volume:07/Issue:03/March-2025 Impact Factor- 8.187 www.irjmets.com

Fig 4: Software Stack for Distributed Training [6]

Beyond training itself, large-scale machine learning workflows also rely on robust checkpointing mechanisms to mitigate the risk of failures. Checkpointing is a technique in which the model's current state—including weights, optimizer parameters, and metadata—is periodically saved to disk. In the event of an interruption due to hardware failures, power outages, or software crashes, training can resume from the most recent checkpoint rather than restarting from scratch. This preserves compute resources and prevents significant financial losses associated with long-running training jobs. High-performance storage infrastructure is essential for efficient checkpointing, with modern data centers leveraging parallel file systems such as Lustre, GPFS (IBM Spectrum Scale), or distributed object storage solutions.

Following the pre-training phase, the next critical step in the machine-learning pipeline is fine-tuning. Fine-tuning leverages the pre-trained model weights as a baseline and trains the model on a domain-specific dataset the user provides. This process significantly enhances the model's performance and accuracy on the user's specific data, allowing it to generate more relevant and context-aware responses. [7]

Unlike pre-training, which requires massive computational resources due to the scale of the dataset and the need for large-scale distributed training, fine-tuning is computationally less demanding. The infrastructure requirements vary based on the size of the fine-tuning dataset and the complexity of the model. Still, fine-tuning can be efficiently performed on smaller servers, often leveraging a few high-performance GPUs rather than an entire datacenter-scale cluster.

Once the model is fine-tuned, the next critical step is deployment. Depending on the use case—whether serving thousands, millions, or even billions of users—the deployment strategy must be carefully designed to balance cost, performance, and user experience metrics. Unlike pre-training, which is computationally intensive but latency-tolerant, inference requires real-time responsiveness, often demanding an entirely different data center architecture optimized for low-latency request handling.

Inference data centers are public-facing and must be designed to handle unpredictable traffic loads efficiently. Load balancing mechanisms, such as global traffic distribution and autoscaling, ensure that resources are dynamically allocated based on real-time demand. Additionally, specialized caching strategies, such as KV (key-value) caching for transformer-based models, can drastically reduce redundant computations and improve throughput. These optimizations collectively enhance the scalability and responsiveness of the model, ensuring that it can serve users efficiently across diverse geographies and applications.

# International Research Journal of Modernization in Engineering Technology and Science (Peer-Reviewed, Open Access, Fully Refereed International Journal)

Volume:07/Issue:03/March-2025

**Impact Factor- 8.187**

www.irjmets.com

Let's dive a bit deeper into the server-level design. (Other levels are below the data center level, like clusters and pods. We ignore them because the concepts of data center design can be used with slight changes, but the server-level design is completely different as the GPUs are tightly connected rather than in different nodes.)

#### III. SERVER DESIGN

#### Server Design Evolution and Standardization

The definition of a server has evolved significantly in recent years, particularly as computing environments become increasingly distributed and interconnected. Traditionally, a server refers to a single machine with one or more processors (CPUs) and memory. However, the concept has become more fluid with the growing complexity of modern systems, particularly in the context of machine learning and artificial intelligence (AI). The software often treats CPUs and GPUs from different nodes as part of the same system, facilitating the distributed nature of contemporary workloads. We define a server as any system where all components, including CPUs, GPUs, memory, and storage, are interconnected via a common Printed Circuit Board (PCB). This definition includes modern systems where multiple nodes are linked, yet the hardware components appear as a unified system to the software stack. The evolution of server architecture for machine learning has been further standardized by initiatives such as the Open Compute Project (OCP) [8]. OCP has played a significant role in streamlining hardware specifications, ensuring that components from different vendors can be easily integrated. Historically, server designs varied widely among different vendors, with each client having custom electrical and mechanical layouts that defined how components were placed within a chassis. This variability led to inefficiencies in production, as custom designs required extensive research, development, and validation. With the explosive growth of AI applications and the need for rapid scaling, this divergence in server designs became a bottleneck. Standardizing server designs through initiatives like OCP has alleviated many of these issues. Open-sourcing hardware specifications have enabled companies to focus on large-scale manufacturing, which has driven down production costs, reduced the time to market, and optimized supply chain operations. The result has been more efficient scaling of AI systems to meet the ever-growing demand for computational power. The key component in these systems is the GPU, which executes the heavy computational workloads associated with training and inference tasks. The baseboard for GPUs, or UBB (OCP) or HGX (NVIDIA), is the foundation for the interconnection of multiple GPUs on a single system. Each GPU board, known as OAM (OCP) or SXM (NVIDIA), houses the GPUs that carry out the computational tasks.

Focusing on the GPU component, these baseboards are typically designed to accommodate multiple GPUs—usually four or eight, depending on the specific GPU architecture. The GPUs within these systems are connected by high-bandwidth data transfer links, such as NVIDIA's NVLink or AMD's Infinity Fabric. These interconnects provide the necessary data throughput and low-latency communication required for high-performance computing tasks, especially those involved in training large machine learning models or performing inference on complex datasets. The GPUs are often tightly coupled, sharing memory resources and working in parallel to execute computations more efficiently. This interconnection between GPUs is crucial in distributed systems, where workloads are partitioned across multiple GPUs to maximize performance. The ability to communicate efficiently between GPUs on the same baseboard or across multiple nodes is essential for reducing latency and increasing throughput, both of which are critical for AI applications.

While this article does not explore the fine-tuning and inference phases in detail, it is important to understand their roles within the machine learning lifecycle. Pre-trained models are typically used as a starting point for direct inference or further fine-tuning. Inference is applying a pre-trained model to new data to generate predictions or decisions. On the other hand, fine-tuning involves taking a pre-trained model and adapting it to a specific use case or domain by training it on a smaller, domain-specific dataset. Fine-tuning is generally considered the final phase of model training, where the model's parameters are adjusted to better fit the particular requirements of the task at hand. The key advantage of fine-tuning is that it requires far less data than pre-training, often only a few thousand to a million data points, making it feasible for organizations with limited access to massive datasets. Unlike pre-training, which may involve datasets spanning terabytes of information, fine-tuning can be accomplished on a smaller scale with relatively lower computational resources. This makes fine-tuning more accessible and cost-effective for many organizations. Typically, a data center of a similar or smaller scale compared to the one used for pre-training is sufficient for fine-tuning. Once the model

# International Research Journal of Modernization in Engineering Technology and Science (Peer-Reviewed, Open Access, Fully Refereed International Journal)

Volume:07/Issue:03/March-2025

**Impact Factor- 8.187**

www.irjmets.com

has been fine-tuned and the appropriate weights have been obtained, the model can be deployed for inference, which can occur on various hardware platforms, such as GPUs, TPUs, CPUs, FPGAs, or ASICs. Each of these hardware platforms offers unique performance, scalability, and cost trade-offs. While this article focuses primarily on GPUs, it's important to note that there is a growing diversity of hardware configurations available to handle the demands of modern AI applications. A full exploration of these alternatives would require a separate discussion, as each has strengths and challenges.

### **GPU-to-GPU Communication Technologies**

One critical aspect of running AI models across multiple servers is the need for efficient GPU-to-GPU communication, particularly when fine-tuning or performing inference on large datasets. In a distributed environment, data must be shared between GPUs on different servers, and maintaining high throughput and low latency is essential to avoid bottlenecks that can hinder model performance. To facilitate this, tools such as PyTorch's Distributed package manage communication across GPUs, enabling the synchronization of model parameters and data across multiple nodes. At the core of these tools are libraries like NCCL (NVIDIA Collective Communications Library) and RCCL (Radeon Collective Communications Library), which provide essential GPU-to-GPU communication primitives. These libraries offer fundamental operations like Gather, Scatter, and Reduce. The Gather operation allows data to be retrieved from one or more GPUs, while Scatter distributes data across GPUs. The Reduce operation is particularly useful for optimizing communication efficiency, as it enables data reduction and transfer to be performed simultaneously, reducing the overall time and bandwidth required for communication. These communication primitives ensure that distributed training and inference processes run smoothly, enabling models to scale across multiple GPUs and servers without significant overhead. Without these communication optimizations, the benefits of distributing workloads across GPUs would be diminished, as data transfer and synchronization overheads could become the limiting factor.

#### **Inference Optimization Techniques**

Processing a single query at a time can be highly inefficient when performing inference. This inefficiency arises because the time required to process one query is often equivalent to the time required to process multiple queries simultaneously. For instance, processing 16 or 32 queries on the same server may take the same time as processing a single query, leading to underutilization of computational resources. To address this issue, inflight batching increases throughput without significantly impacting latency. Inflight batching involves grouping multiple queries together and processing them in parallel, allowing for more efficient hardware use while maintaining a low-latency response. This technique is particularly useful in real-time AI applications, where multiple user queries need to be processed concurrently without introducing significant delays. The challenge, however, lies in the unpredictability of when user queries will arrive, making it difficult to preemptively batch queries for optimal processing. Advanced scheduling algorithms and dynamic batching techniques have been developed to address this issue, ensuring that inference tasks are performed as efficiently as possible, even in the face of fluctuating query arrival rates.[9] In addition to inflight batching, other optimizations include model quantization, which reduces the precision of the model weights and activations (e.g., from FP32 to FP16 or INT8) to speed up inference and reduce memory consumption without significant loss in accuracy[10]. Pruning is another technique, removing less important model weights or neurons to reduce the model size and computational load, thereby improving inference efficiency[11]. Furthermore, hardware-specific optimizations can dramatically improve inference throughput, such as using Tensor Cores on NVIDIA GPUs or specialized accelerator chips like TPUs and FPGAs. Finally, caching and data prefetching mechanisms are also critical for reducing data transfer overhead, especially when inference involves accessing large datasets or when the same queries are repeated frequently.

#### **Key-Value Caching for Transformer Models**

A particularly important optimization technique for inference in transformer models is key-value (KV) caching[12]. In natural language processing (NLP) tasks, where transformers are commonly used, the KV cache stores intermediate key and value pairs generated during input token processing. Only the newly generated tokens must be computed when processing a new input query, while the previously computed key-value pairs are reused. This significantly reduces the computation required for each new token in autoregressive tasks, such as text generation, where each new word depends on the preceding ones. The system can avoid redundant

# International Research Journal of Modernization in Engineering Technology and Science (Peer-Reviewed, Open Access, Fully Refereed International Journal)

Volume:07/Issue:03/March-2025

**Impact Factor- 8.187**

www.irjmets.com

computation by caching these key-value pairs, improving efficiency and reducing latency, particularly in long sequence tasks. The KV cache is often stored in high-speed memory to minimize access time, and optimizations to manage its size and update frequency can further enhance performance. Combining KV caching with other techniques, such as inflight batching, quantization, pruning, and hardware acceleration, can substantially improve inference efficiency, making systems better suited for real-time, high-throughput AI applications, particularly those involving large-scale language models. Let's go deeper into the hardware and software for each GPU.

### IV. GPU DESIGN

### The Role of Modern GPUs in AI/ML Acceleration

Modern GPUs are high-throughput computing powerhouses originally designed to accelerate computer graphics rendering. Unlike CPUs, which are optimized for low-latency, general-purpose computations, GPUs excel at performing massively parallel operations on large datasets, making them well-suited for applications beyond graphics. Over the past two decades, GPUs have evolved from dedicated graphics processors to general-purpose accelerators, demonstrating exceptional efficiency in scientific computing, high-performance computing (HPC), and artificial intelligence (AI).

Fig 5: Modern GPU Architecture for AI [11]

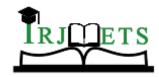

One of the most transformative applications of GPUs has been in accelerating AI and machine learning (ML) workloads. The computational demands of deep learning models, particularly large-scale neural networks, align closely with the GPU's ability to perform parallelized matrix and tensor operations. Unlike earlier GPU architectures such as Pascal, which were primarily designed with rasterization and shading for graphics workloads, modern GPUs—such as NVIDIA's Blackwell architecture—have been specifically engineered to maximize performance for AI. The Blackwell GPU features several hardware advancements tailored for deep learning, including dedicated matrix multiplication units (tensor cores), specialized tensor memory accelerators for efficient data movement, and support for emerging low-precision numerical formats such as FP4 and FP8, which enhance computational efficiency while maintaining accuracy in AI workloads.

### Computational Requirements of Large Language Models (LLMs)

The computational complexity of large language models (LLMs) has grown exponentially with increasing model sizes. Training such models requires orders of magnitude more computing than inference, primarily due to the iterative process of gradient-based optimization, which involves forward and backward passes through billions

# International Research Journal of Modernization in Engineering Technology and Science (Peer-Reviewed, Open Access, Fully Refereed International Journal)

Volume:07/Issue:03/March-2025

**Impact Factor- 8.187**

www.irjmets.com

of parameters across massive datasets. For example, training the Llama 3 model with 405 billion parameters demands approximately 40 exaFLOP-days—a measure of computational work indicating that 40 exaFLOPs of compute power are needed continuously for an entire day to complete training.

To contextualize this requirement, consider the capabilities of the NVIDIA Blackwell GB100 GPU, which delivers 3.5 petaFLOPs of FP4 computing. Given that 1 exaFLOP equals 1,000 petaFLOPs, training Llama 3 within a single day would require:

$40 \times 10^3$  petaFLOP-days ÷ 3.5 petaFLOPs per GPU ≈ 134,000 GPUs

This estimate highlights the sheer scale of computational resources required for state-of-the-art AI training.[4] For comparison, a modern high-performance CPU, such as the AMD EPYC Bergamo 9754, which features 128 cores and delivers 10.9 teraFLOPs of compute, would take significantly longer to train the same model. Even if 100,000 such CPUs were used in parallel, the training process would take approximately 1.18 years to complete. This stark contrast underscores why GPUs have become the de facto standard for AI workloads—by accelerating computations that would otherwise take years to mere days, and they enable rapid iteration cycles and feasible deployment of cutting-edge models.

Processo Required Training Time for Model **Specifications** Performance r Type Units LLaMA 3 (405B) **NVIDIA Blackwell** AI-optimized 3.5 petaFLOPs **GPU** ~134,000 1 day GB100 accelerator (FP4) AMD EPYC 10.9 teraFLOPs CPU 100,000 128 cores ~1.18 years Bergamo 9754

**Table 1:** Computational Requirements Comparison for LLaMA 3 (405B) Training [4]

## The Critical Role of GPU Software Optimization

While hardware advancements drive raw computational capability, achieving optimal performance from a GPU requires highly efficient software. Theoretical peak FLOPs alone do not guarantee real-world performance—how effectively software utilizes available hardware resources determines the actual throughput of deep learning workloads. If a deep learning model achieves only 50% of the GPU's theoretical peak performance, training time effectively doubles, or twice the number of GPUs would be required to meet the same deadline. This inefficiency has severe consequences:

Time-to-Market Delays: AI research and product development rely on fast iteration cycles. If training takes twice as long, teams may miss critical deployment windows, limiting opportunities for refinement and innovation.

Exponential Cost Increases: Since GPU clusters are expensive to operate, requiring twice the number of GPUs significantly raises infrastructure costs, making large-scale AI training financially impractical for many organizations.

Given these constraints, optimizing GPU workloads to leverage matrix multiplication units (tensor cores) entirely is crucial. However, writing efficient GPU code requires specialized expertise in hardware-aware programming, making it inaccessible to many developers. To address this, NVIDIA provides CUTLASS (CUDA Templates for Linear Algebra Subroutines and Solvers), a high-performance CUDA library that enables developers to implement efficient custom network layers without manually writing low-level GPU kernels. CUTLASS provides optimized building blocks for deep learning and scientific computing workloads, ensuring modern GPUs achieve near-theoretical efficiency in AI applications [13].

## V. THE EVOLUTION OF DEEP LEARNING COMPILERS

Beyond libraries like CUTLASS, the emergence of deep learning compilers such as Triton[14] and TVM[15] has revolutionized GPU programming by automating the process of generating optimized GPU kernels. These compilers take high-level descriptions of neural network operations and lower them into hardware-optimized CUDA kernels, reducing the need for hand-tuned implementations.

# International Research Journal of Modernization in Engineering Technology and Science (Peer-Reviewed, Open Access, Fully Refereed International Journal)

Volume:07/Issue:03/March-2025

**Impact Factor- 8.187**

www.irjmets.com

Triton is a cutting-edge deep-learning compiler that enables users to define custom kernels with minimal effort and optimizes them to run efficiently on GPUs. It abstracts away the complexity of low-level GPU programming, making it easier to implement advanced models like attention mechanisms or custom layers while achieving near-peak GPU performance.

TVM provides an end-to-end optimization stack that targets various hardware backends, including GPUs. It lowers high-level model descriptions into optimized code for multiple architectures, significantly improving performance while reducing the need for low-level hardware-specific tuning. Both Triton and TVM lower the barrier to entry for AI researchers and engineers, allowing them to achieve high-performance training without deep GPU programming expertise.

These advances in compiler technology enable automated, fine-grained optimization that maximizes hardware utilization and accelerates the development cycle for AI models.

## The Historical Impact of GPUs on Deep Learning

A landmark achievement catalyzed the adoption of GPUs for deep learning: the first deep neural network to surpass human performance in image classification was trained using NVIDIA GPUs. In 2012, a team from the University of Toronto, led by Geoffrey Hinton, Ilya Sutskever, and Alex Krizhevsky, trained the AlexNet model using GPUs to win the ImageNet Large Scale Visual Recognition Challenge (ILSVRC) [16]. This breakthrough demonstrated that GPUs could accelerate deep learning by orders of magnitude compared to traditional CPU-based training, sparking a widespread shift toward GPU-powered AI research.

Since then, GPUs have remained indispensable for AI across both training and inference. Advances in hardware, including tensor cores and memory accelerators, combined with improvements in software—such as optimized libraries like CUTLASS, cuDNN, cuBLAS, deep learning compilers like Triton and TVM, and new numerical formats—have fueled exponential progress in AI capabilities. As models grow in size and complexity, GPU acceleration will remain a cornerstone of AI innovation, enabling the next generation of breakthroughs in natural language processing, computer vision, and generative AI.

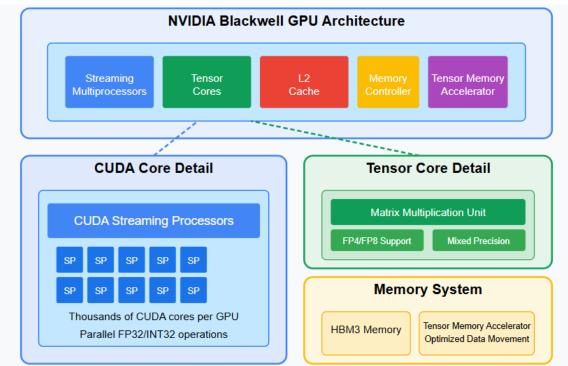

#### VI. AI IN DATACENTER DESIGN

#### **AI-Driven Data Center Optimization**

AI is used in multiple areas throughout the data center and machine learning pipeline to solve key challenges mentioned in the article. One significant area is model architecture search and optimization. Designing the best neural network architecture for a given task requires extensive experimentation, which can be time-consuming and computationally expensive. AI-driven techniques like Neural Architecture Search (NAS) automate this process by exploring different configurations, reducing human effort, and accelerating model development[17].

Another critical challenge is data curation and preprocessing. Poor-quality data can degrade model performance, and manually preparing datasets is labor-intensive. AI-powered data cleaning and augmentation techniques, including self-supervised learning and automated anomaly detection, help curate high-quality datasets. AI also detects biases, fills in missing data, and optimizes tokenization strategies, ensuring models are trained on the most effective inputs.

Distributed training optimization is another area where AI plays a crucial role. Large-scale training requires efficient parallelization to maximize GPU utilization and minimize communication overhead. AI-driven workload scheduling and reinforcement learning-based resource allocation optimize how workloads are distributed across thousands of GPUs. Additionally, AI-guided auto-tuning adjusts hyperparameters dynamically, improving training efficiency without excessive manual intervention.

Networking and communication efficiency are also essential in large-scale AI workloads. Inter-GPU communication bottlenecks can slow training in large clusters, making efficient data transfer necessary. AI-driven network congestion prediction models optimize routing strategies, reduce packet collisions, and improve overall data transfer efficiency. These techniques help ensure multi-GPU systems operate smoothly, minimizing idle time and improving overall throughput.

Fault detection and recovery are crucial for maintaining system reliability. Hardware failures and crashes can result in significant computation loss if not properly managed. AI-based predictive maintenance models analyze hardware telemetry data to anticipate failures before they occur. Additionally, intelligent checkpointing

# International Research Journal of Modernization in Engineering Technology and Science (Peer-Reviewed, Open Access, Fully Refereed International Journal)

Volume:07/Issue:03/March-2025

**Impact Factor- 8.187**

www.irjmets.com

strategies, guided by AI, determine the optimal checkpointing frequency, balancing reliability and storage efficiency while minimizing downtime.

AI is also instrumental in fine-tuning models efficiently. Fine-tuning requires human-labeled data, which is expensive and slow to generate. Active learning helps by using AI to identify the most informative data points, reducing the amount of labeled data needed while maintaining accuracy. AI-driven transfer learning strategies enhance efficiency by enabling models to reuse pre-trained knowledge, reducing computational costs.

Inference and latency optimization are other key challenges that AI helps address. Deploying models at scale requires low-latency inference while minimizing hardware costs. AI-powered model compression techniques such as quantization, pruning, and distillation reduce model size without sacrificing accuracy. Additionally, AI-driven caching strategies—such as KV caching for transformers—improve response times by avoiding redundant computation and reducing memory access delays.

Finally, AI is critical in data center resource management and load balancing. Cloud data centers must dynamically allocate resources to meet varying workloads while minimizing costs. AI-powered autoscaling algorithms predict demand and adjust compute resources dynamically. Moreover, reinforcement learning-based schedulers optimize GPU allocation across different workloads, improving utilization and reducing power consumption. These AI-driven strategies ensure that computing resources are used efficiently, lowering operational costs while maximizing performance.

In summary, AI is not just the training workload but also an essential tool for optimizing nearly every aspect of the machine learning pipeline. From model design and training to deployment and infrastructure management, AI-driven solutions enhance efficiency, reduce costs, and improve system reliability.

#### Industry Applications: Google's TPU and NVIDIA's GPU Design

Google has leveraged AI to design its Tensor Processing Unit (TPU), a custom AI accelerator designed for machine learning workloads, particularly for deep learning tasks. Google employed AI techniques, such as reinforcement learning and neural architecture search, to optimize the design of the TPU architecture. This method was used to improve the placement of various components, such as matrix multiplication units and memory management, to achieve high throughput for tensor operations at a low power consumption. Google's AI-driven approach helped accelerate the design process, enabling faster iterations and optimizing the TPU's architecture.[23][24]

NVIDIA has been a major player in using AI for chip design, particularly in its DGX systems and GPUs, including the A100 and H100 GPUs. AI techniques are used throughout the design of the GPUs to optimize power efficiency, maximize throughput, and ensure that the hardware can handle the enormous parallel workloads required by modern AI applications. For example, NVIDIA uses AI to optimize memory allocation and interconnect designs within GPUs to minimize latency and maximize data throughput between cores. In addition, AI is applied in AutoML (Automated Machine Learning) to assist in developing new architectures for tasks like neural network training and inference acceleration.[18][19][20][21][22]

Fig 6: Recursive Relationship Between AI and Infrastructure

## International Research Journal of Modernization in Engineering Technology and Science (Peer-Reviewed, Open Access, Fully Refereed International Journal)

Volume:07/Issue:03/March-2025 Impact Factor- 8.187 www.irjmets.com

### VII. CONCLUSION

Data center design for AI represents a specialized discipline requiring careful alignment between application characteristics and infrastructure capabilities. The article demonstrates how the computational demands of modern AI workloads, particularly large language models, necessitate purpose-built systems rather than general-purpose computing environments. GPU technology has emerged as the cornerstone of these specialized systems, with modern architectures specifically engineered to maximize performance for AI through dedicated matrix multiplication units and specialized memory accelerators. The synergy between hardware advancements and software optimization has enabled exponential progress in AI capabilities, reducing training times from years to days. Furthermore, AI has become an essential tool for optimizing nearly every aspect of the machine learning pipeline, from model architecture search to fault detection and resource management. As AI evolves, this recursive relationship—where AI improves the infrastructure designed to support it—will likely drive further innovations in data center design, creating increasingly efficient systems capable of supporting even more complex models and applications.

#### VIII. REFERENCES

- [1] Chunqiang Tang, "Meta's Hyperscale Infrastructure: Overview and Insights," 2025, Available: https://cacm.acm.org/research/metas-hyperscale-infrastructure-overview-and-insights/

- [2] Yiheng Liu et al., "Understanding LLMs: A Comprehensive Overview from Training to Inference," 2024, Available: https://arxiv.org/abs/2401.02038v2

- [3] Yian Zhang et al., "When Do You Need Billions of Words of Pretraining Data?," 2020 Available: https://arxiv.org/abs/2011.04946

- [4] Aaron Grattafiori et al., "The Llama 3 Herd of Models," 2024, Available https://arxiv.org/abs/2407.21783

- [5] Adam Paszke et al., "PyTorch: An Imperative Style, High-Performance Deep Learning Library," 2019 Available: https://arxiv.org/abs/1912.01703

- [6] PyTorch, "Distributed communication package torch.distributed," Available: https://pytorch.org/docs/stable/distributed.html

- [7] Jesse Dodge et al., "Fine-Tuning Pretrained Language Models: Weight Initializations, Data Orders, and Early Stopping," 2020, Available: https://arxiv.org/abs/2002.06305

- [8] Open Compute Project, "Scaling Innovation Through Collaboration!" Available: https://www.opencompute.org/

- [9] Jiacheng Liu et al., "A Survey on Inference Optimization Techniques for Mixture of Experts Models," 2025, Available: https://arxiv.org/abs/2412.14219

- [10] Hao Wu et al., "Integer Quantization for Deep Learning Inference: Principles and Empirical Evaluation," 2020, Available: https://arxiv.org/abs/2004.09602

- [11] Yihui He, "Pruning Very Deep Neural Network Channels for Efficient Inference," 2022, Available: https://arxiv.org/abs/2211.08339

- [12] Reiner Pope et al., "Efficiently Scaling Transformer Inference," 2022, Available: https://arxiv.org/abs/2211.05102

- [13] Lucas Wilkinson, "Improvements for: Groupwise scaling along M for FP8 gemm," Available: https://github.com/NVIDIA/cutlass

- [14] Philippe Tillet et al., "Triton: an intermediate language and compiler for tiled neural network computations," 2019, Available: https://dl.acm.org/doi/10.1145/3315508.3329973

- [15] Tianqi Chen et al., "TVM: An Automated End-to-End Optimizing Compiler for Deep Learning," 2018, Available: https://arxiv.org/abs/1802.04799

- [16] Alex Krizhevsky et al., "ImageNet Classification with Deep Convolutional Neural Networks," 2012, Available:

https://papers.nips.cc/paper\_files/paper/2012/hash/c399862d3b9d6b76c8436e924a68c45b-Abstract.html

- [17] Barret Zoph et al., "Neural Architecture Search with Reinforcement Learning," 2017, Available: https://arxiv.org/abs/1611.01578

# International Research Journal of Modernization in Engineering Technology and Science (Peer-Reviewed, Open Access, Fully Refereed International Journal)

Volume:07/Issue:03/March-2025 Impact Factor- 8.187 www.irjmets.com

- [18] NVIDIA, "TSMC and Synopsys Bring Breakthrough NVIDIA Computational Lithography Platform to Production," 2024, Available: https://nvidianews.nvidia.com/news/tsmc-synopsys-nvidia-culitho

- [19] Mingjie Liu et al., "ChipNeMo: Domain-Adapted LLMs for Chip Design," 2023, Available:. https://research.nvidia.com/publication/2023-10\_chipnemo-domain-adapted-llms-chip-design

- [20] Anthony Agnesina, et al., "AutoDMP Optimizes Macro Placement for Chip Design with AI and GPUs," 2023, Available:https://developer.nvidia.com/blog/autodmp-optimizes-macro-placement-for-chip-design-with-ai-and-gpus/

- [21] Chia-Tung (Mark) Ho, et al., "NVCell 2: Routability-Driven Standard Cell Layout in Advanced Nodes with Lattice Graph Routability Model," 2023, Available: https://research.nvidia.com/publication/2023-03\_nvcell-2-routability-driven-standard-cell-layout-advanced-nodes-lattice-graph

- [22] Hao Chen, et al, "Reinforcement Learning Guided Detailed Routing for Custom Circuits," 2023, Available: https://research.nvidia.com/publication/2023-03\_reinforcement-learning-guided-detailed-routing-custom-circuits

- [23] Anna Goldie et al., "How AlphaChip transformed computer chip design," 2024, Available: https://deepmind.google/discover/blog/how-alphachip-transformed-computer-chip-design/

- [24] Samuel K. Moore, "Ending an Ugly Chapter in Chip Design Study tries to settle a bitter disagreement over Google's chip design AI," 2023, Available: https://spectrum.ieee.org/chip-design-controversy